信息科学与工程

频率合成技术广泛应用于通信、航空航天、仪器仪表等领域.一般情况下,产生正弦波都采用频率合成技术,常用的频率合成技术有直接频率合成、锁相频率合成和直接数字频率合成等[1].

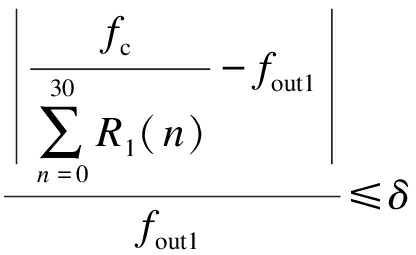

一直以来直接数字频率合成都用FPGA、CPLD、DSP等控制器来实现,但局限性比较大,只能用于硬件设计,不能作为专用芯片使用,存在电路复杂、功耗高、分辨率低等缺点.本文采用的阶梯波产生算法是一种新型的直接数字频率合成技术,算法具有频率分辨率高、频率切换速度快、相位连续、相位噪声低及频率稳定度高等优点.既可以配合带有DAC功能的单片机使用,又可以作为一种专用芯片使用,具有很强的通用性,是一种新的频率合成方法.目前所得的频率合成范围大约为0~100 Hz[2],频率分辨率为1 Hz[3],而本文设计的阶梯波产生电路能够产生1 200、2 200 Hz的频率,分辨率约为0.000 03 Hz.

频率合成技术的典型应用就是HART协议仪表.HART协议在现有的4~20 mA模拟信号上叠加数字信号,属于模拟系统向数字系统转变的过渡产品[4].HART协议采用Bell 202通信标准的FSK频移键控技术,传输速率为1 200 bit/s.在2FSK中,载波的频率变化随二进制基带信号在f1和f2两个频率点间变化.载波具体表达式为

(1)

调制模式下,输入为1时,输出调制为1 200 Hz的正弦波;当输入为0时,输出调制为2 200 Hz的正弦波.

FSK阶梯波发送电路主要由模拟部分和数字部分组成.数字部分采用一种阶梯波算法产生温度码;模拟部分是一种温度码DAC,用来输出阶梯波.

阶梯波产生算法是一种由频率控制字DIN输入1或者0来控制输出阶梯波频率的算法,输出频率表达式为

(2)

(3)

式中:![]() 为每种频率的总步长;fc为系统时钟频率分频后的频率;δ为频率误差;fout1=1 200 Hz;fout0=2 200 Hz.在本次设计中,时钟频率f=3.686 4 MHz,如果fc=f,则整个电路的功耗将非常高,不符合当今低功耗的发展趋势,所以需对f进行分频.DIN输入0或者1时,每个相位点的步长是不同的,所以会输出不同的频率.分频情况下每种频总的步长及对应的计算结果如表1所示.

为每种频率的总步长;fc为系统时钟频率分频后的频率;δ为频率误差;fout1=1 200 Hz;fout0=2 200 Hz.在本次设计中,时钟频率f=3.686 4 MHz,如果fc=f,则整个电路的功耗将非常高,不符合当今低功耗的发展趋势,所以需对f进行分频.DIN输入0或者1时,每个相位点的步长是不同的,所以会输出不同的频率.分频情况下每种频总的步长及对应的计算结果如表1所示.

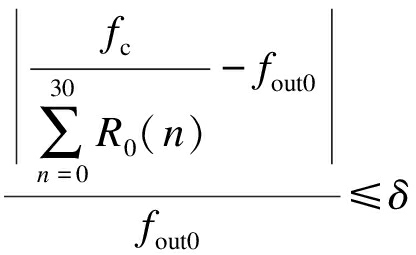

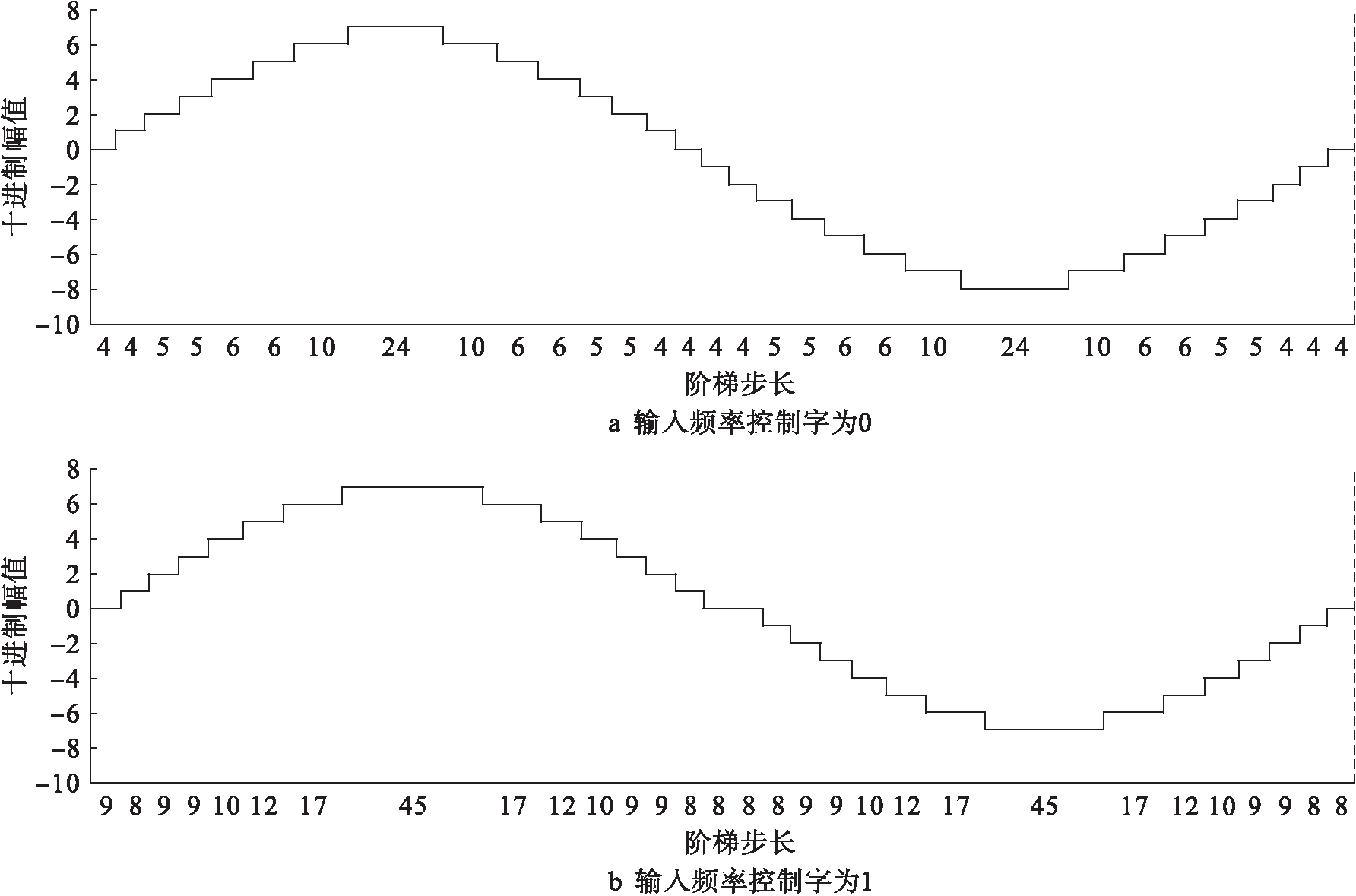

表1 ∑R计算结果及其对应的频率

Tab.1 ∑R calculation results andcorresponding frequency

分频数∑R0∑R1fout0/Hzfout1/Hz0167530722200.831200283715362202.15120044187682204.79120082093842204.781200161041922215.381200

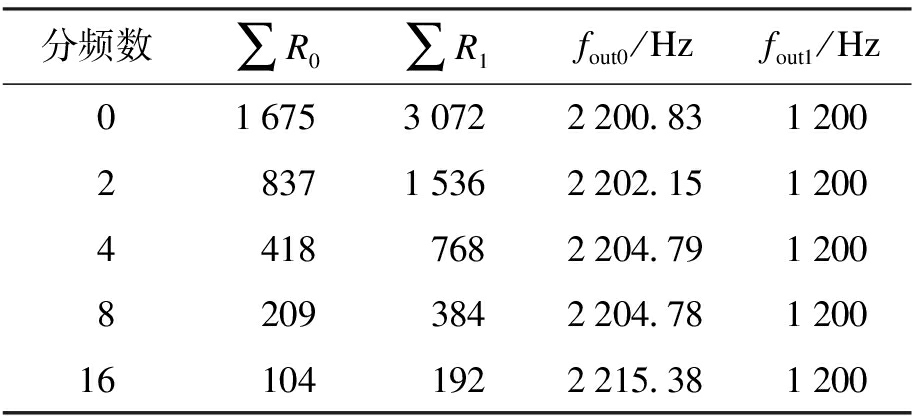

从表1中可以看出,不分频和2分频fout0结果更加接近2 200 Hz,但是由于频率过高系统功耗会大,所以不宜采用.4分频和8分频fout0的结果比较接近,但是从系统的简化程度来说,8分频时系统将更简单而且功耗低,所以最后采用8分频时的∑R0和∑R1值作为DIN为0和1时的总步长,δ频率误差约为千分之一.本文根据DAC的分辨率,在0~2π中利用反三角函数各取30个相位点Xi(i=1,2,…,30),各个步长是通过查找Xi+1-Xi值在0~2π所占比例适当调整后确定,具体步长分配如图1所示.

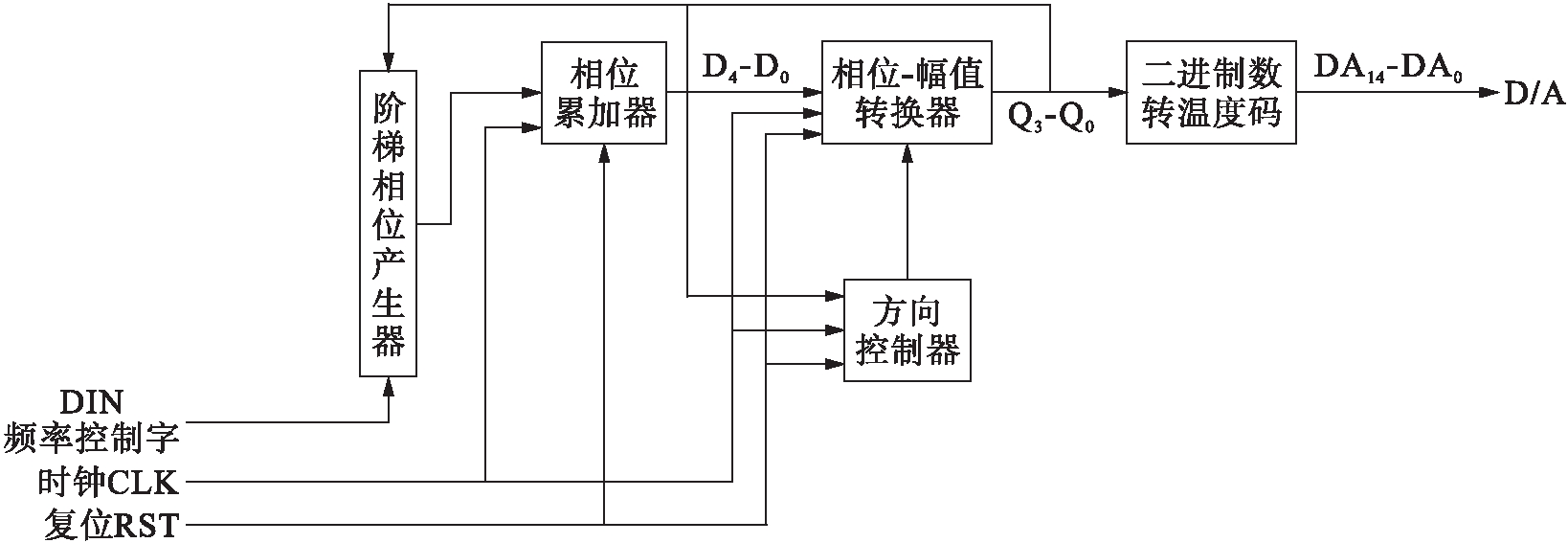

相位连续的FSK阶梯波发送电路主要由数字电路部分阶梯相位产生器、相位累加器、相位![]() 幅值转换器、方向控制器、二进制数转温度码电路以及模拟电路部分温度码DAC数模转换器构成.信号发送电路图如图2所示.

幅值转换器、方向控制器、二进制数转温度码电路以及模拟电路部分温度码DAC数模转换器构成.信号发送电路图如图2所示.

当频率控制字DIN输入时,阶梯相位产生器首先判断是否为0,若是则通知相位累加器;否则产生两个脉冲后再通知相位累加器.实际上阶梯相位产生器是一个数据选择器,选择每个阶梯的步数Ri,然后将对应阶梯的步数Ri交给相位累加器.当DIN为1,幅值达到步长为45时,相位累加器无法识别,因此在这里有个特殊处理来保证在833 μs内能够完成一次周期的相位幅值转换.

相位累加器是一个预置计数器,计数器的值是阶梯相位产生器下一个阶梯的步长值,具体计算过程如下:

1) 当阶梯相位产生一个阶梯的步长时,相位累加器将对此阶梯步长做减法计算.

2) 当减到0时,通知相位![]() 幅值转换器完成一次相位到幅值的转换.每完成一次幅值转换,相位

幅值转换器完成一次相位到幅值的转换.每完成一次幅值转换,相位![]() 幅值转换器就会通知阶梯相位产生器产生下一个阶梯的步长,并交给相位计数器,来完成下一个幅值的转换.

幅值转换器就会通知阶梯相位产生器产生下一个阶梯的步长,并交给相位计数器,来完成下一个幅值的转换.

图1 连续相位FSK阶梯波发送电路步长分配

Fig.1 Step size assignment of continuous phase FSK ladder wave transmission circuit

图2 连续相位FSK信号发送电路框图

Fig.2 Block diagram of continuous phase FSK signal transmission circuit

3) 相位![]() 幅值转换是一个可逆计数器并且受方向控制器的控制,其工作过程如下:

幅值转换是一个可逆计数器并且受方向控制器的控制,其工作过程如下:

① 当方向控制器为0时,则代表up状态,即阶梯波上升,幅值为-8~7;

② 当方向控制器为1时,则代表down状态,即阶梯波下降,幅值为7~-8;

③ 当Q3-Q0=7时,方向则由up状态向down转换,逆变计数器则由7减到-8;

④ 当Q3-Q0=-8时,方向则由down向up转换,逆变计数器则由-8加到7.

如果过程中频率控制字DIN变化,将继续按照当前方向进行,并且相位累加器继续按照上一个DIN值的步长减数.当步长减为0时,下一拍的步长和频率将变为当前DIN值的步长和频率.

当相位![]() 幅值转换完成后,幅值将送给二进制数转温度码电路,将幅值对应的4位二进制数转换为15位的温度码.二进制数转温度码的过程是一个查表的过程,每个幅值二进制数将对应一个温度码.

幅值转换完成后,幅值将送给二进制数转温度码电路,将幅值对应的4位二进制数转换为15位的温度码.二进制数转温度码的过程是一个查表的过程,每个幅值二进制数将对应一个温度码.

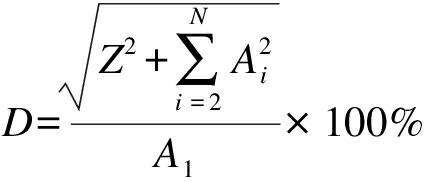

失真是频率合成技术的重要参数,正弦波形下,利用Ai表示谐波的有效值幅度(i=2,3,…,N),Z表示噪声及非谐波分量的有效值幅度,则失真度[5]可定义为

(4)

经过测量,输出信号频率在1 200 Hz和2 200 Hz时的失真度约为3%,可以证明利用此算法得出结果的准确性大大提高.

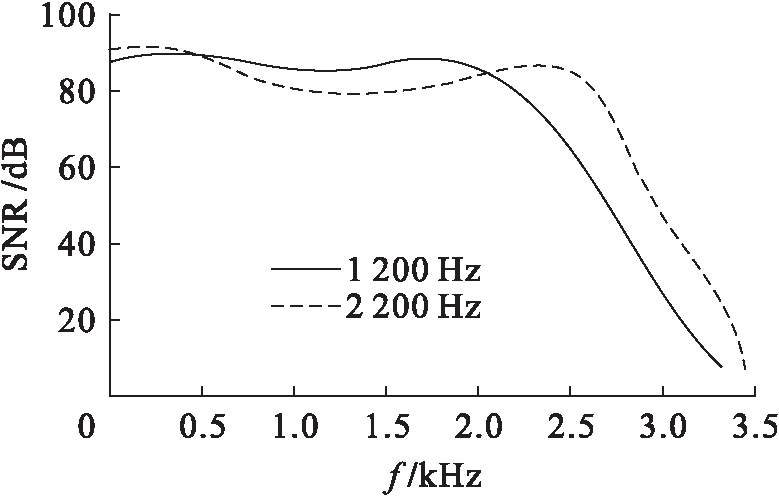

DAC字宽决定了其分辨率,满量程时,字宽与信噪比SNR关系表达式为

SNR=6.02B+1.76 dB

(5)

式中,B为DAC字宽.本文DAC字宽为15位,所以信噪比为92 dB.信噪比与频率关系图如图3所示,频率在1 200、2 200 Hz时,信噪比约为90 dB.

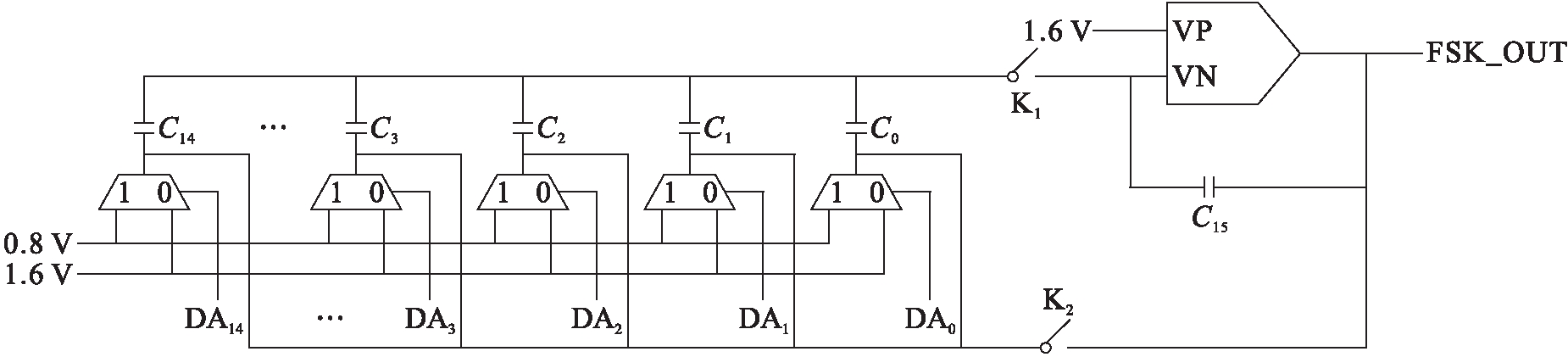

相位![]() 幅值转换器输出温度码后,需要输入一个DAC再输出阶梯波,本文采用了一种温度码DAC,具体电路如图4所示.温度码的优点是当数字输入码每次变化1位,输出信号也只变化1位,即使在转换时,也仅有一个二选一开关发生转换,这样输出电流中的毛刺就得以有效控制[6].

幅值转换器输出温度码后,需要输入一个DAC再输出阶梯波,本文采用了一种温度码DAC,具体电路如图4所示.温度码的优点是当数字输入码每次变化1位,输出信号也只变化1位,即使在转换时,也仅有一个二选一开关发生转换,这样输出电流中的毛刺就得以有效控制[6].

图3 信噪比与频率关系

Fig.3 Signal to noise ratio and frequency relationship

图4 温度码DAC

Fig.4 Temperature code DAC

温度码DAC[7-9]电路由一种高驱动能力放大器、15个二选一开关及K1和K2两个开关组成;数字电容下部由1个二选一开关构成,一种状态选择到数字开关上,另一种选择到输出上;数字电容的公共端会被一直保持在1.6 V,而电容的另一端则由数字开关选择;K1闭合,数字开关变化一次后电容的二选一开关连接到输出上,这时16个电容并联,原来的公共端电压保持不变,电荷进行再分配;K2闭合,可以得到输出端的电压,该电压会保持在C15上,最后输出,完成一次动作.

本文采用Mentor公司的ADMS混仿工具进行仿真,运放及DAC的偏置采用了理想电压源、电流源,DAC电路采用Hspice网表形式,阶梯波产生电路采用Verilog代码形式,并配有测试文件.

测试文件中定义时钟分度值为1 ns,由于外接晶振频率为3.686 4 MHz,时钟模块首先对时钟进行了2分频,所以进入到数字模块的时钟实际频率为1.843 2 MHz,时钟周期为542 ns,时钟每经过271 ns翻转一次.

初始状态所有器件都处于复位状态,DIN在空闲状态时置高电平,D4-D0=11000,Q3-Q0=0000,DA14-DA0=000000011111111,数字部分电路处于发送状态.

经过100 μs数字模块复位解除,DIN引脚每经过833 μs发送一个数据,DA14至DA0引脚开始发送阶梯波数据至外部DAC转换器模块,最后,由DAC输出明显可以看到,当DIN数据端为1时,阶梯波频率低;当DIN数据端为0时,阶梯波频率高.

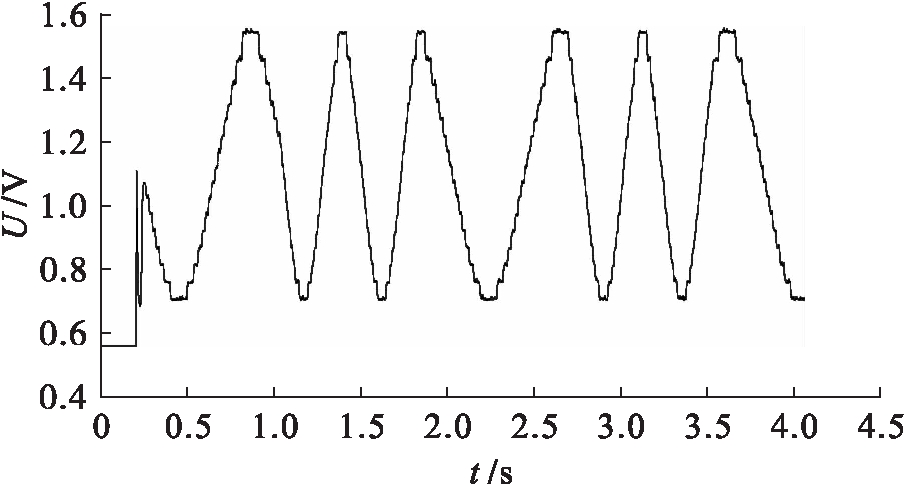

通过ADMS软件将Hspice网表、Verilog网表和测试文件连接起来进行数模混合仿真,得出最终结果如图5所示(DIN为00100时的输出结果).

图5 混合仿真

Fig.5 Hybrid simulation

本文设计了一种适用于HART协议仪表的相位连续的FSK[10-11]信号发送电路,该电路由连续相位的阶梯波产生电路和温度码DAC电路组成,阶梯波产生电路对于频率控制字的变化有很强的感知能力,电路结构简单,功耗约为0.14 mA,信噪比约为92 dB.这种频率合成技术既可以配合带有DAC功能的单片机使用,又可以作为一种专用芯片使用,具有很强的通用性.本文设计的相位连续的FSK信号发送电路解决了实际工程应用中遇到的正弦波失真度高和频率误差大的问题,此电路失真度约为3%,频率误差为千分之一,整个电路工作稳定,性能优良.经过模数混合仿真验证,该电路实现了发送功能,并且各项指标均达到预期效果,能够产生相位连续的FSK信号阶梯波,满足工程实际要求.

[1]潘志浪.基于FPGA的DDS信号源的设计 [D].武汉:武汉理工大学,2007:1-59.

(PAN Zhi-lang.Design of DDS signal source based on FPGA [D].Wuhan:Wuhan University of Technology,2007:1-59.)

[2]牛耕,陈思宇,于继翔.基于DDS技术的正弦交流信号源的设计 [J].现代电子技术,2012,35(3):52-56.

(NIU Geng,CHEN Si-yu,YU Ji-xiang.Design of sine signal source based on DDS technology [J].Modern Electronics Technique,2012,35(3):52-56.)

[3]施羽暇,吕威,李一晨.基于DDS技术的正弦信号发生器 [J].信息技术,2007,31(1):14-16.

(SHI Yu-xia,LÜ Wei,LI Yi-chen.Sine signal generator based on DDS technology [J].Information Technology,2007,31(1):14-16.)

[4]阳宪惠.现场总线技术及其应用 [M].北京:清华大学出版社,2008:357.

(YANG Xian-hui.Fieldbus technology and its application [M].Beijing:Tsinghua University Press,2008:357.)

[5]梁志国,朱济杰,孙璟宇.正弦信号源波形失真的一种精确评价方法 [J].计量学报,2003,24(2):144-148.

(LIANG Zhi-guo,ZHU Ji-jie,SUN Jing-yu.An accurate evaluation method for waveform distortion of sinusoidal signal source [J].Acta Metrologica Sinica,2003,24(2):144-148.)

[6]吕超群.0.18 μm CMOS高速高精度电流舵DAC的研究与设计 [D].南京:南京邮电大学,2013:1-60.

(LÜ Chao-qun.0.18 μm CMOS high speed and high precision current steering DAC research and design [D].Nanjing:Nanjing University of Posts and Telecommunications,2013:1-60.)

[7]Konczykowska A,Jorge F,Dupuy J Y,et al.84 GBd (168 Gbit/s) PAM-4 3.7 V pp power DAC in InP DHBT for short reach and long haul optical networks [J].Electronics Letters,2015,51(20):1591-1593.

[8]Radulov G I,Quinn P J,van Roermund A H M.A 28-nm CMOS 1V 3.5 GS/s 6-bit DAC with signal-independent delta-I noise DfT scheme [J].IEEE Transactions on Very Large Scale Integration Systems,2015,23(1):44-53.

[9]Huang H,Heilmeyer J,Grozing M,et al.An 8-bit 100-GS/s Distributed DAC in 28-nm CMOS for optical communications [J].IEEE Transactions on Mi-crowave Theory & Techniques,2015,63(4):1211-1218.

[10]Saadeh W,Awais M,Bin A,et al.A pseudo OFDM with miniaturized FSK demodulation body-coupled communication transceiver for binaural hearing aids in 65 nm CMOS [J].IEEE Journal of Solid-State Circuits,2017,52(3):757-768.

[11]Thirunarayanan R,Ruffieux D,Scolari N,et al.A 51.4 Mb/s FSK transmitter employing phase domain digital synthesizer with 1.5 μs start-up for energy efficient duty cycling [C]//European Solid-State Circuits Conference.Lausanne,Switzerland,2016:129-132.