嵌入式系统是一种控制或监测机器的专用计算机系统,广泛应用于医疗电子设备、智能家居、物流运输装饰和电力控制系统等多个领域[1-2].为了实现嵌入式系统数据和信息的安全性,密码技术作为信息安全领域的核心技术通常被用于该系统的具体运行中,其主要原理是利用计算复杂性理论,防止攻击者获取系统的数据和信息[3-4].在密码技术的实际应用中,密码算法和协议的设计可以充分保证其理论上的安全性,然而,其最容易被攻击的弱点通常出现在其具体实现细节上.尤其是在具有开放性的嵌入式系统中,攻击者可以轻松得到众多关键运行数据,甚至直接获取算法的密钥,此时,嵌入式系统没有任何安全性可言[5-6],所以,如何提高嵌入式系统中密码算法的安全性是一个亟待解决的系统化问题.为了解决嵌入式系统的安全问题,必须从该类系统的基本组成结构出发,探索安全性较高的轻量实现方案,其具体措施是基于有限的带宽和硬件资源,尽量使用较小的功耗和计算资源实现嵌入式系统所需的安全计算任务[7].在设计安全方案时,需要考虑系统的功耗、存储和面积等多种因素.尤其需要注意的是,由于功耗分析方法具有较高的攻击效率,所以设计该方案时,必须考虑其对功耗分析方法的抵抗能力[8-9].

本文从密码算法的实现准则出发,研究了AES-128算法的实现问题.通过介绍该算法的S盒、行移位和列混合等多个计算部件的实现设计,给出了AES-128算法的实现方案.此外,使用差分功耗分析和相关性功耗分析的方法对该算法进行了多次攻击,并统计其响应结果.结果表明,AES-128算法具有较好的安全性,可以满足嵌入式系统的安全需求.

1 实现准则

在嵌入式系统中,密码算法的实现必须考虑多方面因素,主要包括:1)实现平台需选择的软件或硬件,这是设计人员首要考虑的问题;2)为了保证嵌入式系统的实时性,算法的实现方案应尽可能地提高其吞吐率;3)算法的安全强度是设计实现方案的核心指标,密码算法的实现方案应该可以抵抗软件攻击和旁路攻击等主流攻击方法;4)需考虑算法的灵活性,即当嵌入式系统的某一协议或标准发生较小改变时,算法的实现方案经过微调之后依旧适应系统的运行;5)在算法实现过程中,设计人员应重点考虑密码算法的实现成本,即芯片使用面积、功率消耗和能源消耗等,从而提高系统设备的续航性能.

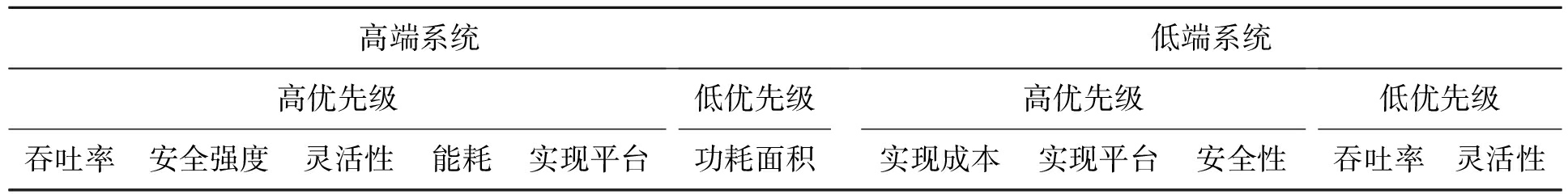

另外,针对不同要求的嵌入式系统,密码算法的实现方案需要考虑的优先级也略有不同.针对低端和高端系统,表1列举了这两种系统的安全实现方案应重点考虑的实现准则.其中,本文主要研究嵌入式系统平台的安全实现方案,而用户认证和信息完整性是方案的主要实现目标,所以,实现成本、功耗、吞吐率和安全性等性能指标是本文需要重点设计和分析的对象.为了平衡功耗、安全性、吞吐率和实现成本等指标,通过比较ECC-GF(2163)和SHA-1等算法,本文选用AES-128算法实现嵌入式系统平台的安全设计.

表1 密码算法实现准则的优先级

Tab.1 Priority of implementation criteria for cryptographic algorithms

高端系统高优先级吞吐率安全强度灵活性能耗实现平台低优先级功耗面积低端系统高优先级实现成本实现平台安全性低优先级吞吐率灵活性

2 AES-128算法实现

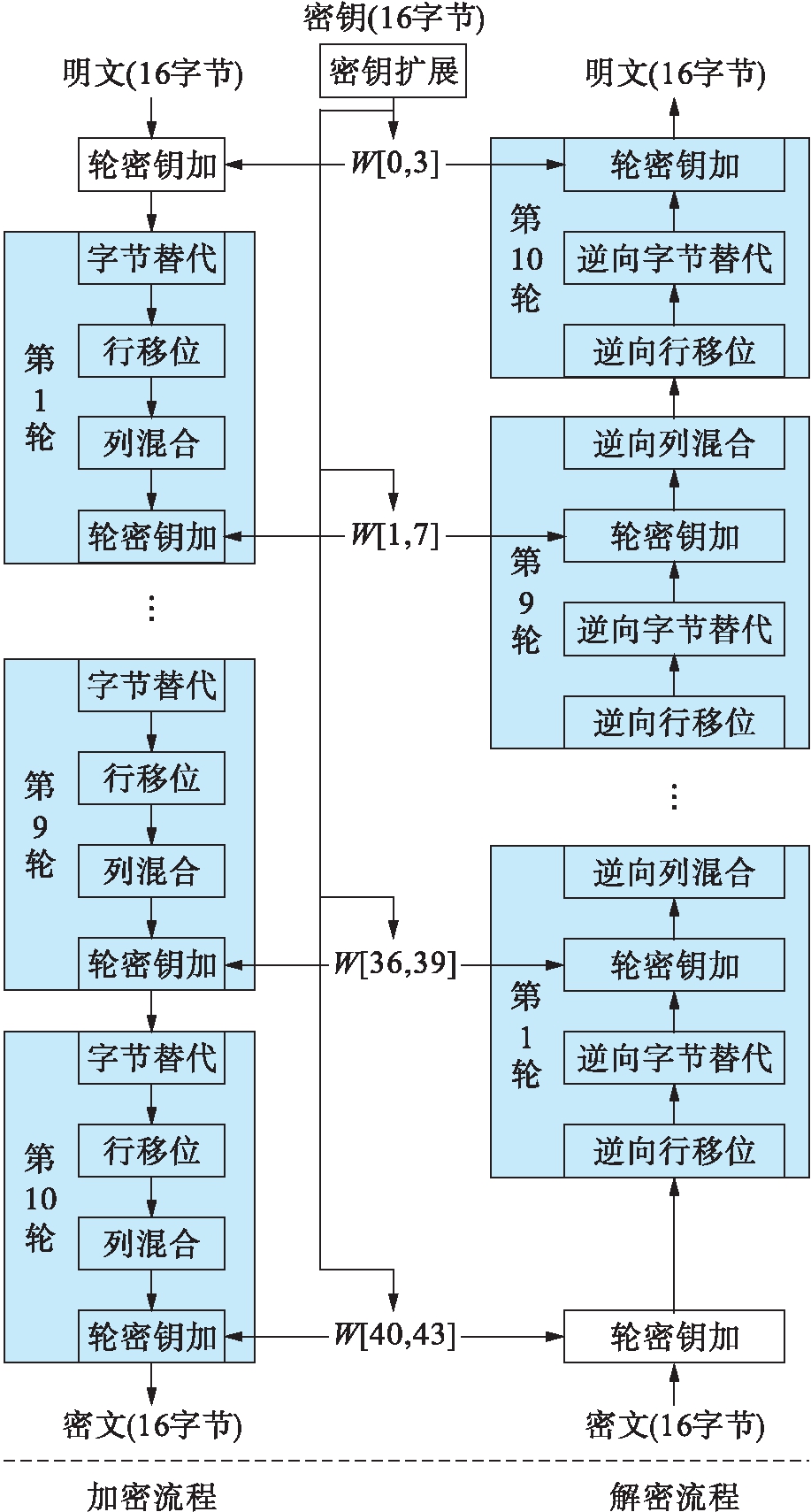

目前,AES标准是对称密码学中最流行的加密算法[10].在其加解密流程中,所有的计算操作主要可分为字节混淆、行移位、列混合和轮密钥加.图1展示了AES算法的加密和解密流程,其中,左边是加密流程,右边是解密流程,其加解密的流程均是10轮.

图1 AES算法加解密流程图

Fig.1 Flow chart of encryption and decryption of AES algorithm

为了实现轻量化的AES-128算法,本文需要实现该算法某一轮的加密或解密运算.其中,由于AES-128算法的加解密流程是相似的,所以只需要实现该算法的一轮加密运算,再对其进行有机组合,即可实现整个算法流程.为了实现该算法的加密轮运算,本文使用了迭代结构,其具体架构如图2所示.

为了实现图2的迭代加密结构,本文一共需要实现20个128位结构的S盒,4个32位结构的S盒和2个8位结构的S盒,这些S盒被用于密钥扩展的数量分别是4、4和1,主要承担了字节替代的计算任务,不同位数的S盒结构是一致的.

图2 AES算法加密轮的迭代结构

Fig.2 Iterative structure of encryption cycle for AES algorithm

2.1 S盒的实现方法

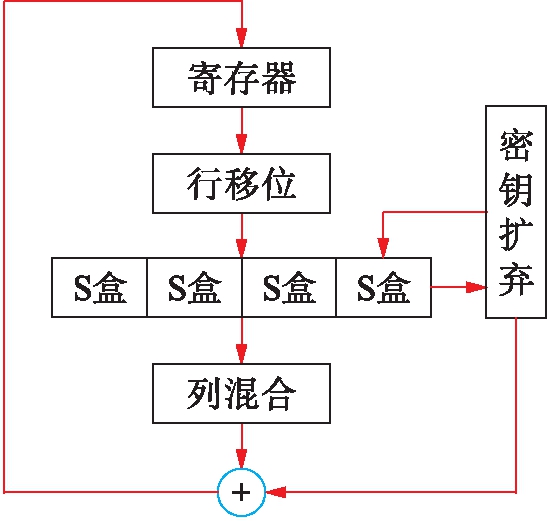

在AES-128算法中,字节替代运算主要由S盒执行.一般而言,AES-128算法的S盒是一个乘法逆变换,也是该算法唯一的非线性变换[11-12].通常,S盒的实现难度是AES算法中最高的.令a表示经过轮密钥加计算的明文,SR表示S盒的乘法逆变换,则S盒的计算公式可表示为

SR[a]=f(g(a))

(1)

式中:g为有限域上的乘法逆运算;f为仿射运算.

AES算法中有两种常用的S盒实现方法[13],第一种方法是查表法,即查找记录运算结果的表格,从而回避繁杂的逻辑运算,然而这种方法的内存要求较高,难以进行复用,不适用于嵌入式系统;第二种方法是基于有限域分解原理的实现方法,即通过将大域的元素分解为小域的元素,经过平方、乘法等一系列的运算,最终得到元素在大域中的乘法逆运算.根据S盒的数学公式,乘法逆运算g的逆变换是其本身,用公式表示为

(2)

综合考虑式(1)、(2)可知,只要实现S盒中的乘法逆运算g、仿射变换f和f-1,就可以实现AES算法中的S盒变换,其电路结构图如图3所示.这种方法非常灵活,实现所需的芯片面积和成本均比较小,所以,该种方法广泛地应用于AES算法中.

图3 S盒的电路结构

Fig.3 Circuit structure of S-boxes

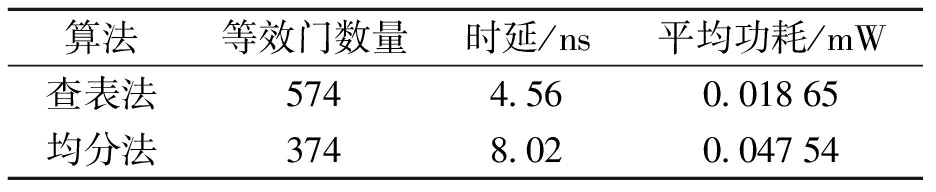

本文使用VHDL语言对这两种实现方法进行对比,通过使用ModelSim仿真手段计算了这两种S盒实现的具体功耗.当时钟频率是10 MHz,输入8位时,其仿真结果如表2所示.

表2 两种S盒实现结构的功耗仿真结果

Tab.2 Power simulation results of two S-boxes implementation structures

算法等效门数量时延/ns平均功耗/mW查表法5744.560.01865均分法3748.020.04754

2.2 行移位

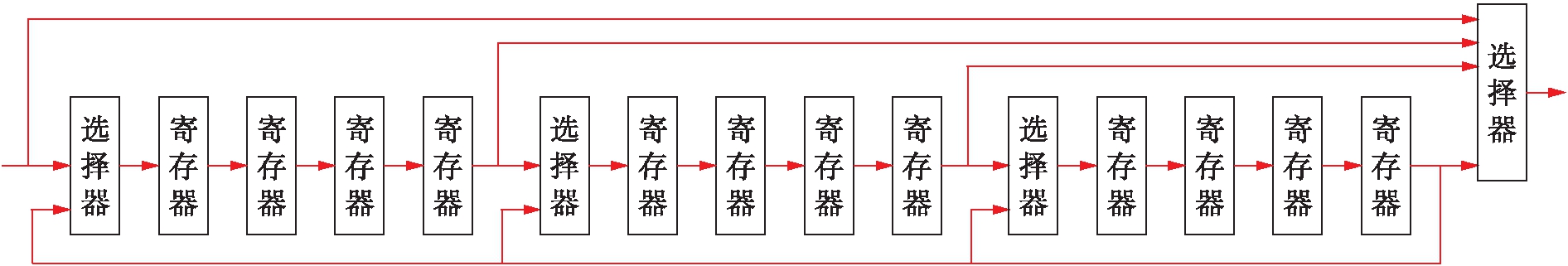

在算法流程中,明文以字节为单位输入到行移位的寄存器中,而相应的部件再次排列寄存器中的字节,即可完成行移位的操作.需要说明的是,这一部分设备在控制时钟信号时,能够完成字节循环双向移动的计算,其电路结构如图4所示.

图4 行移位电路结构图

Fig.4 Structural diagram of row shift circuit

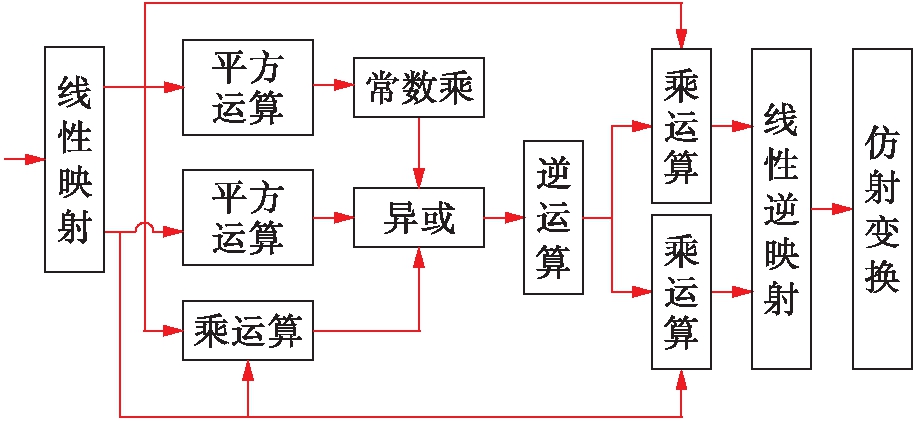

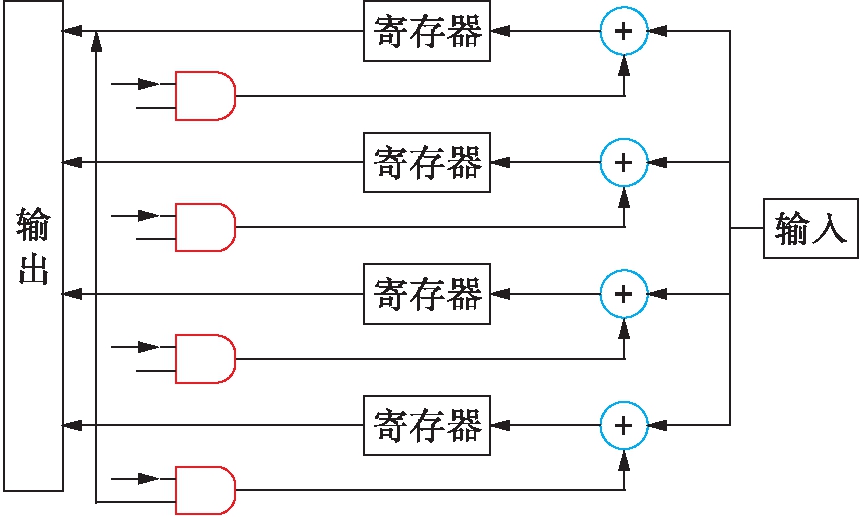

2.3 列混合

当算法进入到列混合运算之后,其中间数据仍然以字节为单位.当数据输入之前,寄存器的使能信号为0,在数据输入和完成时,寄存器的使能信号变为1,同时用相同的乘法系数对数据进行乘法计算,通过添加和循环转移等操作实现列混合的运算,并将其结果存储到寄存器中.计算完成后,其输出结果将被传输到串并转换单元,其电路结构如图5所示.

图5 列混合电路结构图

Fig.5 Structural diagram of column mixing circuit

3 功耗分析

在实现AES-128算法后,为了保证该算法的安全性,本文使用功耗分析对该算法进行了多次攻击测试.功耗分析是一种旁路攻击方法,其攻击方法与电磁分析类似,攻击原理是通过观察和测量的方法,检测加密电路中的多种特征,从而分析和推测算法中的计算与逻辑信息,最终得到其密钥信息,破解其加密算法.

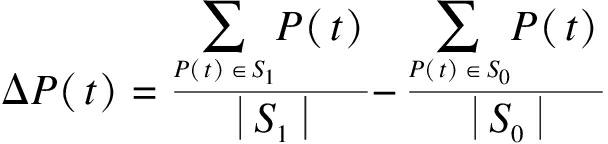

本文主要采用了差分功耗分析(DPA)和相关性功耗分析(CPA)对AES-128算法进行分析与测试.DPA是利用不同的功耗泄露数据进行差异推断的统计分析方法,该方法对平均值做差,以功耗泄露数据为区分函数,其具体分析过程为

(3)

(4)

式中:Pi和Pj为真实功耗泄露数据;HK,i和HK,j分别为S0集合与S1集合的预测功耗泄露参数;K为待攻击的子密钥;P(t)为t时刻的功耗泄露数据.

CPA是一种基于皮尔森相关系数统计的分析方法,该方法通过统计功耗数据和算法中间变量的相关系数,获取相应的密钥信息,其具体分析过程为

(5)

式中:T(t)为算法中的中间变量;E和σ为某变量的期望和方差.

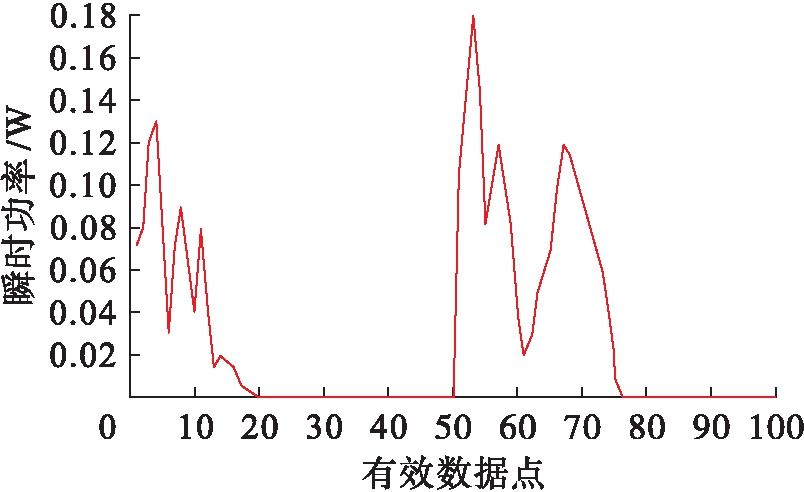

在DPA仿真测试平台上,设置电路的时钟频率为2.5 MHz,其功耗数据的记录周期为1 ns,在每个时钟周期之内,平台可以记录400个数据点.因为DPA的攻击时间处于AES的前两轮,所以本文只需要记录这两轮的功耗数据.由于本文选择了AES-128算法的前两轮进行攻击,所以得到了这两轮的瞬时功耗数据如图6所示.

图6 AES-128算法的瞬时功耗泄露数据

Fig.6 Instantaneous power leakage data of AES-128 algorithm

由图6可知,在输出数据为20~50之后,电路的功耗泄漏趋近于0.在数据达到80以后,电路的功耗泄漏可以忽略不计.这意味着AES-128算法在数据量为0~20、50~77时更容易被分析,而一旦数据量超过80,则该算法基本难以被攻击.利用DPA仿真测试平台,本文对AES-128算法进行了6 000次仿真,其结果基本一致,即当密钥的数据位数超过80之后,DPA就难以获取正确的密钥信息.

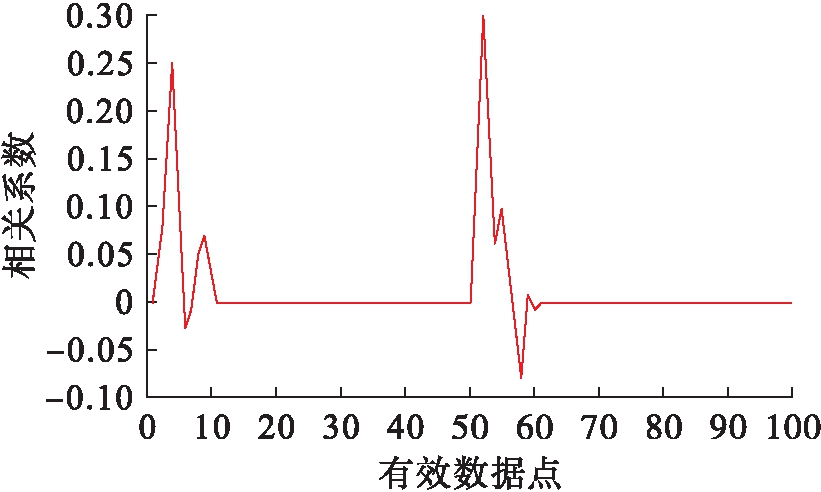

在CPA仿真测试平台上,使用相同的时钟频率和数据周期等参数,本文也进行了类似的测试和分析,得到了预测功耗与实际功耗之间的相关系数随数据个数变化的曲线,结果如图7所示.

图7 相关系数与数据个数的关系图

Fig.7 Relationship between correlation coefficient and number of data

由图7可知,在数据个数达到60之后,则其相关系数就趋近于0.利用CPA仿真测试平台,本文对AES-128算法进行了4 000次仿真,其统计结果大同小异,即当密钥的位数达到60之后,目前的攻击模型便难以得到密钥信息.

根据DPA和CPA的仿真测试结果可知,针对这两种主流的功耗分析方法,AES-128算法的密钥信息很难发生泄露,安全性较好.

4 结 论

针对嵌入式系统的安全问题,本文提出了AES-128算法的轻量实现方案,并对该方案进行了功耗的仿真测试.测试结果表明,AES-128算法具有较好的安全性,但本文还未对该方案进行其他分析方法的测试和攻击,该实现方案可能存在一些未知的安全隐患,所以,如何继续优化AES-128算法的实现方案将是未来研究的方向.

[1] 卢军,张国辉,李国强.一种基于数据分解的AES优化算法设计[J].单片机与嵌入式系统应用,2019,19(4):22-25.

(LU Jun,ZHANG Guo-hui,LI Guo-qiang.An AES optimization algorithm design based on data decomposition[J].Application of MCU and Embedded System,2019,19(4):22-25.)

[2] 林荣智,苗耀锋.基于用户项目特征分组的隐私保护算法[J].沈阳工业大学学报,2018,40(6):72-77.

(LIN Rong-zhi,MIAO Yao-feng.Privacy protection algorithm based on user item feature grouping[J].Journal of Shenyang University of Technology,2018,40(6):72-77.)

[3] 万刘蝉,韦永壮.AES-128的密钥中比特检测及分析[J].桂林电子科技大学学报,2016,36(4):338-341.

(WAN Liu-chan,WEI Yong-zhuang.Bit detection and analysis in key of AES-128[J].Journal of Guilin University of Electronic Science and Technology,2016,36(4):338-341.)

[4] 殷爱菡,王胜凯.基于改进的AES算法的EPON安全方案研究[J].华东交通大学学报,2013(4):35-39.

(YIN Ai-han,WANG Sheng-kai.EPON security scheme research based on improved AES algorithm[J].Journal of East China Jiaotong University,2013(4):35-39.)

[5] 曾小波,易志中,焦歆.基于51核的AES算法高速硬件设计与实现[J].电子科技,2016,29(1):36-39.

(ZENG Xiao-bo,YI Zhi-zhong,JIAO Xin.High-speed hardware design and implementation of AES algorithm based on 51 cores[J].Electronic Science and Technology,2016,29(1):36-39.)

[6] 贺依盟,周亚军.AXI总线加密模块的设计与验证[J].杭州电子科技大学学报,2016(1):57-62.

(HE Yi-meng,ZHOU Ya-jun.Design and verification of AXI bus encryption module[J].Journal of Hangzhou Dianzi University,2016(1):57-62.)

[7] Singh A,Chawla N,Ko J H,et al.Energy efficient and side-channel secure cryptographic hardware for IoT-edge nodes[J].IEEE Internet of Things Journal,2018,2:133-146.

[8] 田道坤,彭亚雄.在区块链中基于混合算法的数字签名技术[J].电子科技,2018,31(7):23-27.

(TIAN Dao-kun,PENG Ya-xiong.Digital signature technology based on hybrid algorithms in block chain[J].Electronic Science and Technology,2018,31(7):23-27.)

[9] Tsai K L,Huang Y L,Leu F Y,et al.AES-128 based secure low power communication for LoRaWAN IoT environments[J].IEEE Access,2018,6:51-66.

[10] 吕慧,赵跃华.基于掩码的AES算法抗二阶DPA攻击方法研究[J].电子设计工程,2015,23(20):31-33.

(LÜ Hui,ZHAO Yue-hua.Research on masking-based AES algorithm against second-order DPA attacks[J].Electronic Design Engineering,2015,23(20):31-33.)

[11] Almazrooie M,Samsudin A,Abdullah R,et al.Quantum reversible circuit of AES-128[J].Quantum Information Processing,2018,17(5):112-129.

[12] 杨威,徐全生,王红,等.基于DSP的软件加密锁的设计与实现[J].沈阳工业大学学报,2007,29(3):347-350.

(YANG Wei,XU Quan-sheng,WANG Hong,et al.Design and implementation of software encryption lock based on DSP[J].Journal of Shenyang University of Technology,2007,29(3):347-350.)

[13] 龚向东,王佳,张准,等.基于FPGA的AES算法硬件实现优化及IP核应用[J].电子设计工程,2017,25(12):1-5.

(GONG Xiang-dong,WANG Jia,ZHANG Zhun,et al.Hardware optimization and IP core application of AES algorithm based on FPGA[J].Electronic Design Engineering,2017,25(12):1-5.)