运算跨导放大器(OTA)是模拟和混合电路中最重要的组成部分之一,例如跨导C滤波器(Gm-C滤波器)、可变增益放大器(VGAs)、压控振荡器(VCOs)和数据转换器等[1-3],这些器件可以产生与差分输入电压成比例的输出电流.近年来,集成电路的设计已经朝着低电源电压和低功耗的方向发展,例如便携式设备,其功率甚至由单个电池提供.因此,众多OTA应具备低电源电压和低功耗的特点,同时具有适当线性度和噪声性能[4-5].

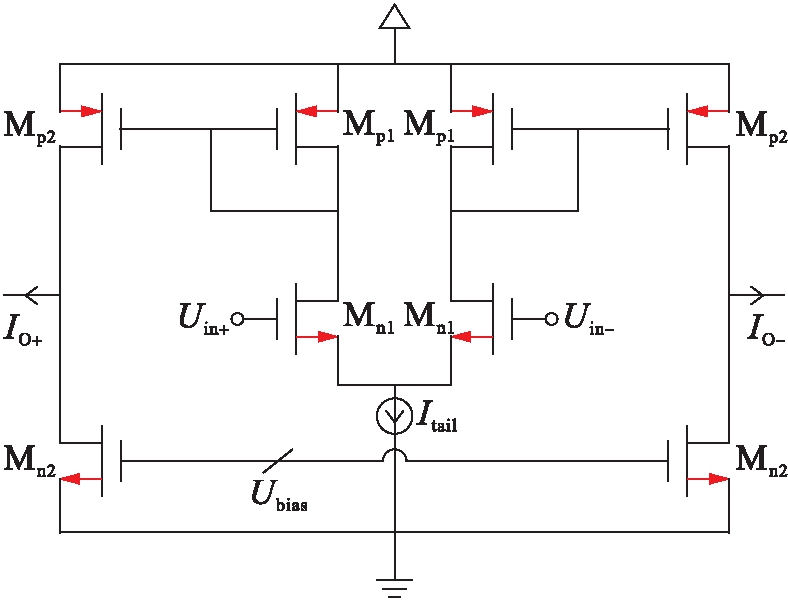

传统的OTA具有全差分(fully differential,FD)结构,如图1所示[6-7],M表示晶体管.FD结构通常基于具有尾电流源的差分对,因此需要一个额外的共模反馈(common mode feedback,CMFB)电路,这也成为全差分电路的主要缺点.因为增加共模反馈电路后增大了放大器的功耗、设计的复杂性、寄生元件数和硅面积消耗量,同时,还降低了电路的线性度和噪声性能.FD结构另一个缺点是跨尾电流源的电压降,其会限制电路的动态范围[8-9].

图1 传统FD OTA

Fig.1 Traditional FD OTA

伪差分(pseudo differential,PD)结构可用于设计低电源电压的OTA,因为其在PD结构中消除了尾电流源,然而PD OTA具有较差的共模抑制比(CMRR)[10-11].为了解决这一问题,本文提出了一种新的基于共模前馈(CMFF)技术的PD OTA.所提出的CMFF技术使得OTA的跨导增益比传统的CMFF OTA增加了一倍甚至更多.将该OTA与传统CMFF OTA进行比较发现,在跨导增益相同的情况下,本文提出的OTA具有较低的功耗.此外,该OTA消除了输出节点处的共模信号,且没有尾电流源和CMFB电路,从而使电路线性度更高,同时改善了电路噪声性能.

1 传统OTA结构

1.1 全差分OTA

传统FD OTA由一个输入差分对和一个尾电流源(Itail)组成.该种结构存在一些缺点,首先尾部电流源的电压降限制了输入信号的共模范围,图1中电源电压的最小值为

Umin=Up1+Un1+Utail

(1)

式中,Utail为尾电流源产生的电压,其在这种结构中是不可避免的.FD结构的第二个问题是会产生额外非线性效应,FD结构的非线性效应是由输入差分对的共源节点处的电压变化引起的,CMFB电路的非线性效应会导致整个OTA的线性性能降低.

1.2 伪差分OTA

与FD结构相比,传统的PD OTA结构可以在较低的电源电压和较高的输入共模范围(ICMR)下正常工作.此外,与FD相比,PD具有更优的线性性能,这是因为在PD结构中,输入差分对的共源节点是接地的,结构主要缺点是在PD结构中共模增益(ACM)几乎等于差模增益(ADM).

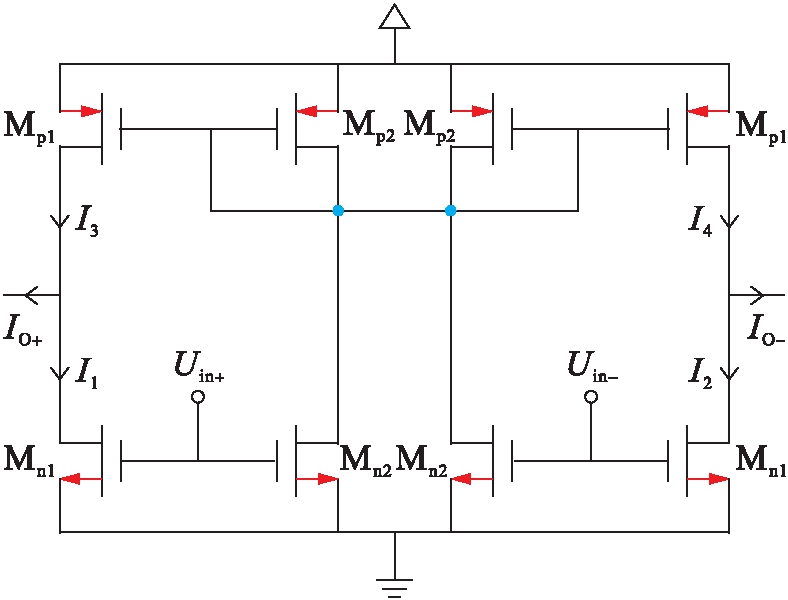

图2为采用共模前馈(CMFF)技术的PD结构基本原理图.CMFF技术用于解决CMRR电路的缺点,其有两条路径:首先晶体管Mn1构成原始路径;其次晶体管Mn2、Mpl、Mp2构成前馈路径.前馈路径将输入共模信号和噪声反向馈送到输出节点,通过检查,前馈路径包含共模信号.但该路径不包含差分模式信号,节点Ucm在差分模式下虚拟接地.图2中来自两个路径的共模信号将在每个输出节点处被消除.

图2 带CMFF的传统PD OTA

Fig.2 Traditional PD OTA with CMFF

在图2中,假设PMOS晶体管和NMOS晶体管具有相同的尺寸,由此可以得到

(2)

式中:g为跨导;m为输出节点.在原始路径的共模和差分模式中,则有

(3)

对于前馈路径的信号,可以得到

gm,n1Uin+=gm,n1Uin-

(4)

在差分模式中,I3和I4为零.在共模输出电流中,则有

(5)

正如图2所分析,共模信号在输出节点处被消除.在差分模式下,共模输出电流为

(6)

因此,该OTA的总跨导为

(7)

PD结构中的CMRR问题在没有尾电流源的情况下得到补偿.

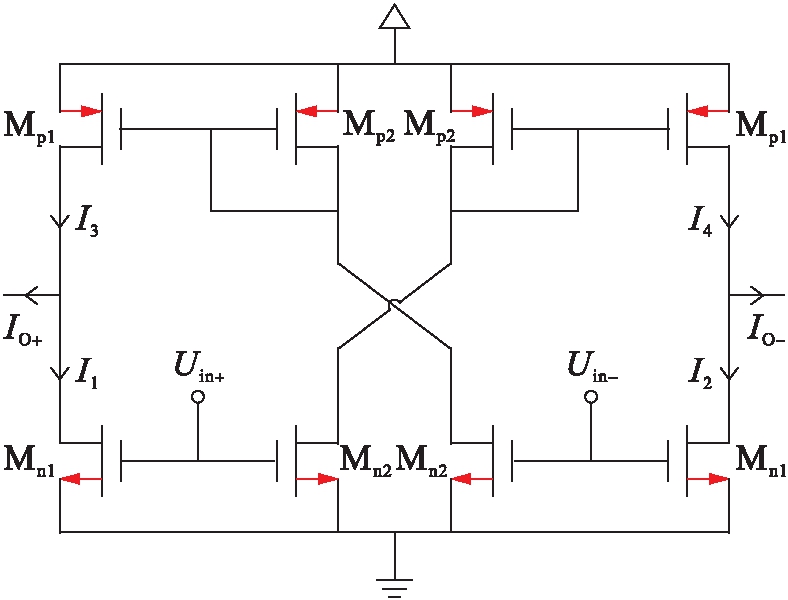

另一种采用CMFF技术的PD结构示意图如图3所示.前馈路径中的两个分支是交叉耦合的,这是图2和图3之间的基本区别.与图2的OTA相比,该种简单的连接导致了前馈路径具有差模信号与共模信号.

图3 带CMFF和交叉连接的传统PD OTA

Fig.3 Traditional PD OTA with CMFF and cross connection

图3中PMOS晶体管和NMOS晶体管的尺寸大小与式(2)给出的PMOS与NMOS尺寸相同.图3中电路原始路径的电流信号为

(8)

前馈路径的电压信号为

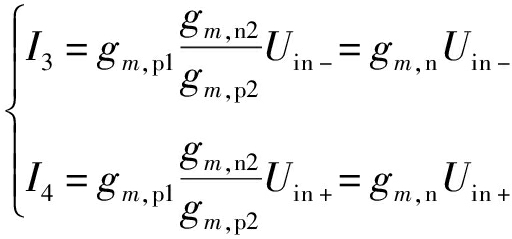

(9)

从式(8)、(9)可以得到,原始路径与前馈路径的信号在输出节点处具有相同的幅度及相反的相位.对于输出电流,则有

(10)

正如预期的设计,共模信号在输出节点处被消除.差分模式的总跨导为

2gm,n

(11)

由式(11)可知,图3结构通过简单的交叉连接可以使电路的跨导加倍.

2 本文提出的OTA

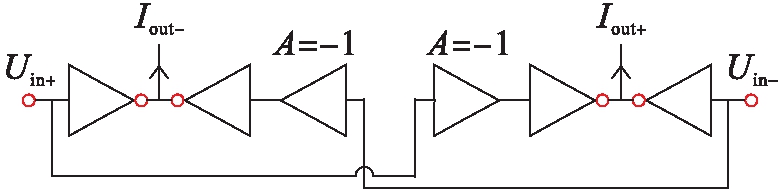

图4为本文所提出的OTA方案图.通过图4可以找到CMFF结构,从两个路径到每个输出节点的信号,均具有相同的幅度和相反的相位,因此,来自两条路径的共模信号在每个输出节点被消除.此外,在差分模式下来自两条路径的信号在每个输出节点被放大.

图4 本文提出的OTA方案图

Fig.4 Scheme of proposed OTA

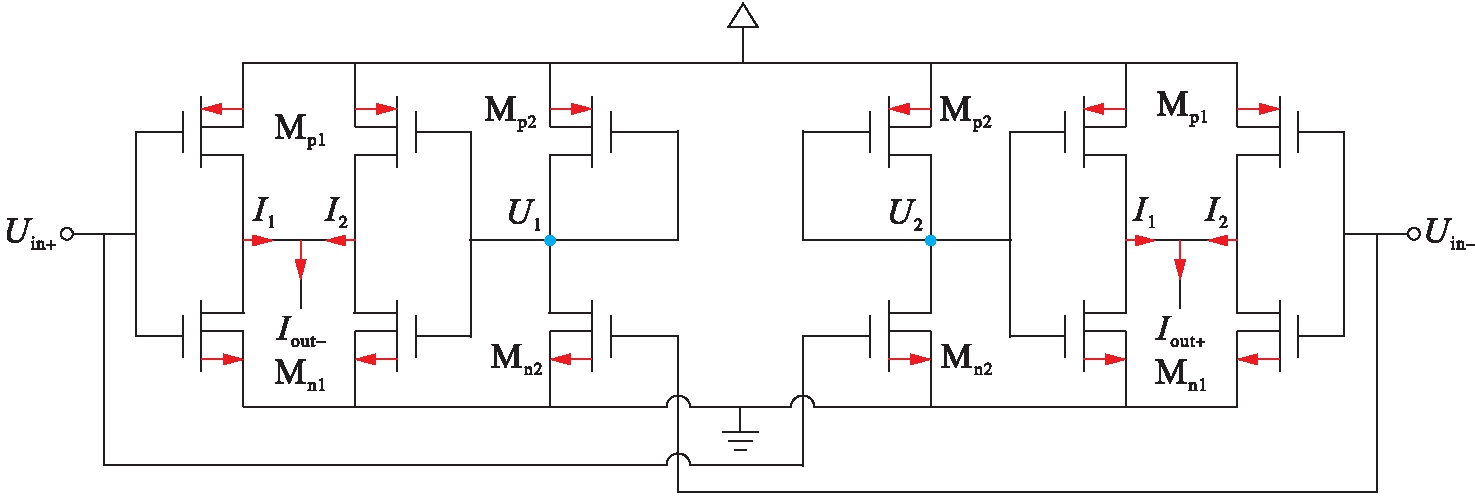

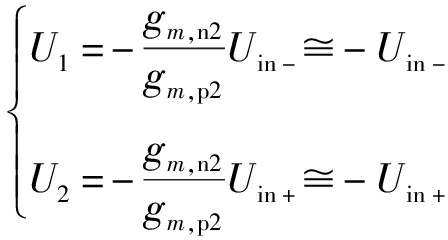

图5为本文所提出的OTA总体电路图.如上所述,从两条路径到每个输出节点的信号大小相等,因此有

gm,p2≅gm,n2

(12)

图5中晶体管Mp2、Mn2的UGS相同且尺寸相当,因此,晶体管M1、M2的跨导值近似相等,可得到

图5 基于CMFF技术的OTA

Fig.5 OTA based on CMFF technique

(13)

所以有

(14)

同样可以得到

(15)

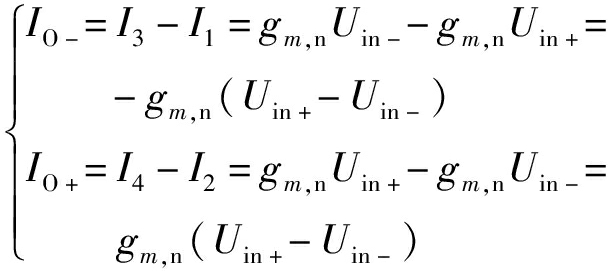

则输出电流可表示为

(16)

因此,本文提出的OTA的整体跨导为

4gm,n1≅4gm,p1

(17)

比较式(17)和式(7)可得,本文提出的OTA的总跨导几乎是文献[6-8]中类似OTA的四倍.同样由式(17)和式(11)可知,与图3相比该跨导增加一倍,但必须考虑所提出的电路具有6个分支,而图3只有4个分支,额外的分支由晶体管Mn2和Mp2制成,这些额外的分支可以缩放以减少电流耗散.通过式(12)可知,晶体管Mn2和Mp2跨导应当只是相等,但它们的数值并不重要.为了产生相同的跨导,所提出的OTA比以前报导的采用CMFF结构的OTA具有更低的功耗,而且从两个路径到输出节点的共模信号被消除,因此,所提出的OTA不需要CMFB电路,故不会降低OTA的线性性能、频率响应及芯片面积.在本文提出的OTA中,可由逆变器确定输入和输出信号摆动,由式(14)可知,晶体管Mn2和Mp2组成的支路电压增益几乎是统一的,且不会降低逆变器的信号摆幅.该电路的输入与输出信号摆幅类似于文献[6-8]中所提及的情况,尽管它具有更高的电压增益.

3 仿真结果分析

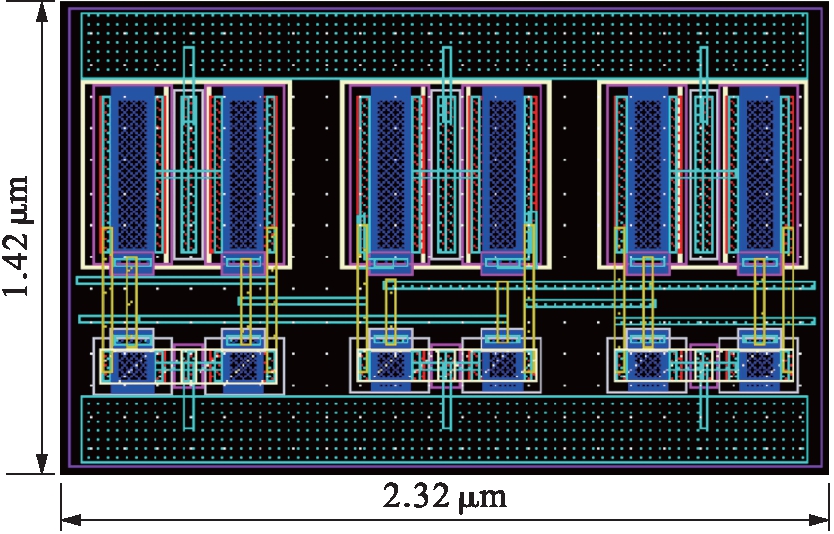

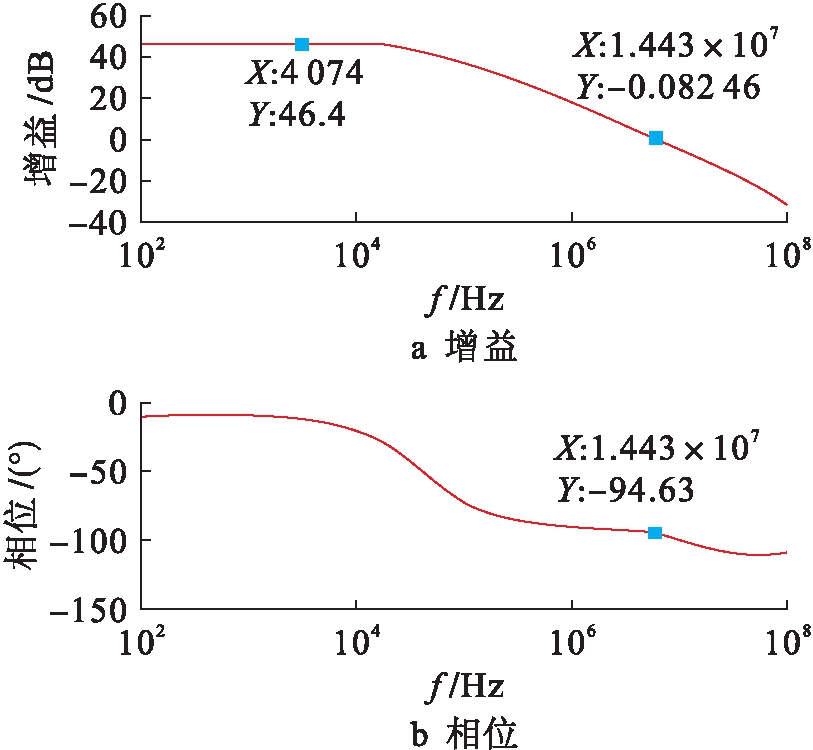

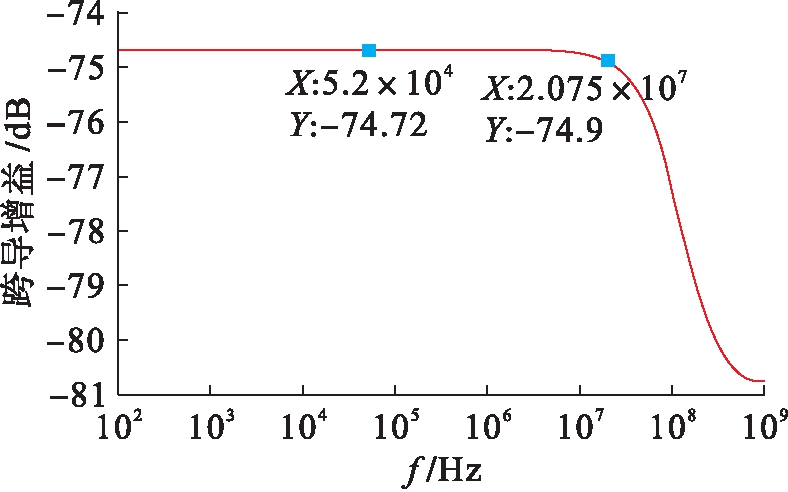

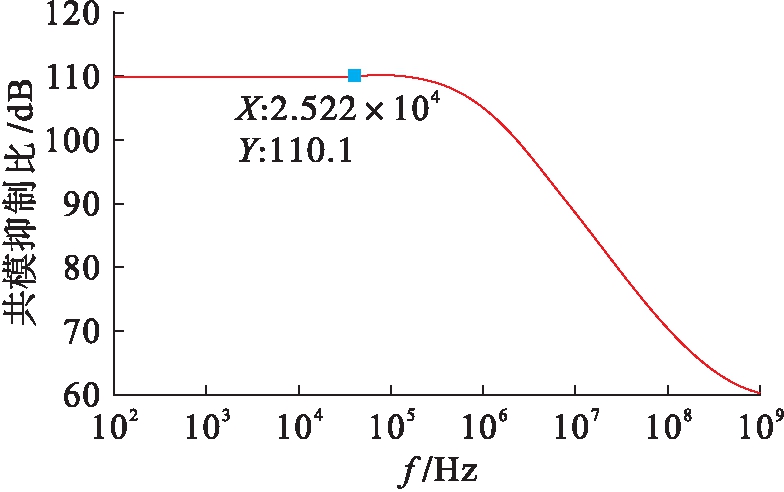

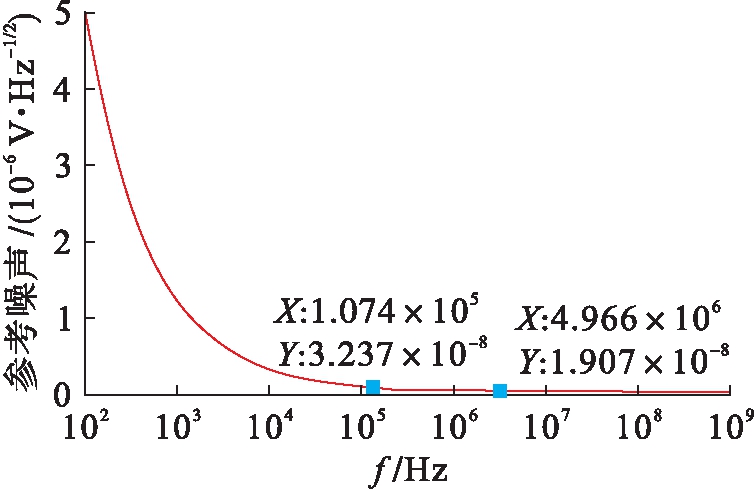

本文提出的OTA采用0.18 标准CMOS技术进行设计和仿真,可在1.2 V单电源电压下工作.OTA的版图布局如图6所示,OTA区域仅为33×10-5 mm2.OTA的增益与相位响应如图7所示,OTA电压增益为46.4 dB,相位裕度为85o,在2 pF负载电容下截止频率为14.5 MHz.OTA的差分跨导增益如图8所示,增益值为-74.7 dB或相当于183.6 μA/V,且在宽频率范围内保持恒定.图9显示了CMRR的频率响应,由图9可以看出,本文所提出的OTA具有较高的CMRR值,CMRR的直流幅度为110.1 dB.此外,本文还评估了输入参考噪声(IRN),由图10可以看出,输入参考噪声在100 kHz时为32.4 nV·Hz-1/2,在5 MHz时为19 nV·Hz-1/2.

图6 本文提出的OTA的版图布局

Fig.6 Layout of proposed OTA

图7 OTA的增益和相位响应

Fig.7 Gain and phase response of OTA

图8 OTA的差分跨导增益

Fig.8 Differential transconductance gain of OTA

图9 CMRR响应曲线

Fig.9 CMRR response curve

图10 本文提出的OTA的IRN

Fig.10 IRN of proposed OTA

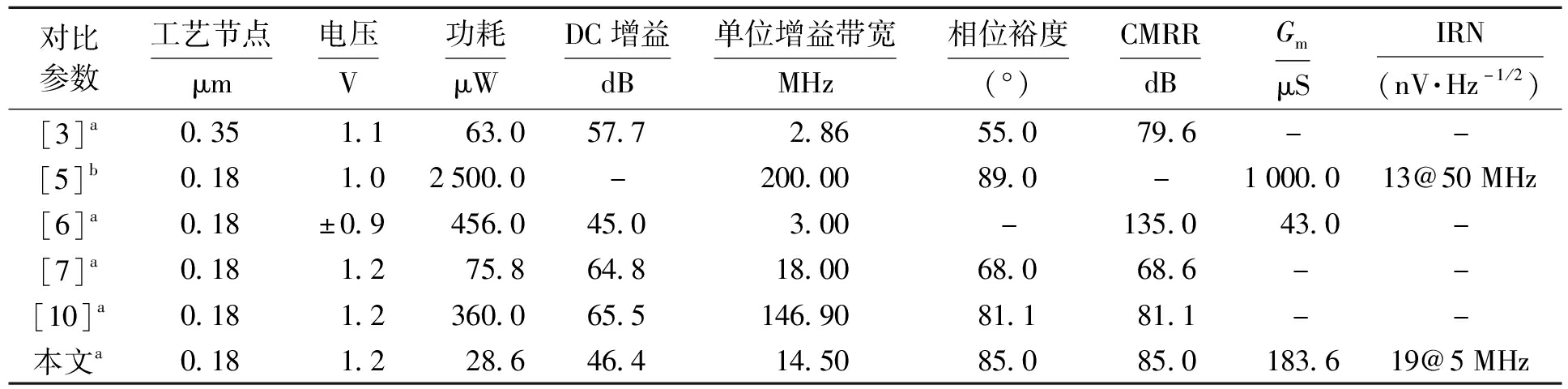

所有上述规格均以23.8 μA电流消耗进行模拟.表1总结了本文所提出的OTA的整体表现,并与现有技术的OTA进行了比较,其中a为仿真结果,b为测量结果.由表1可以看出,本文所提出的OTA在功耗降低的情况下仍具有较高的CMRR值.

表1 本文提出的OTA与文献中OTA的比较

Tab.1 Comparison between OTA proposed in this paper with those reported in literatures

对比参数工艺节点μm电压V功耗μWDC增益dB单位增益带宽MHz相位裕度(°)CMRRdBGmμSIRN(nV·Hz-1/2)[3]a0.35 1.163.057.7 2.8655.079.6--[5]b0.181.02500.0-200.0089.0-1000.013@50MHz[6]a0.18±0.9456.045.03.00-135.043.0-[7]a0.181.275.864.818.0068.068.6--[10]a0.181.2360.065.5146.9081.181.1--本文a0.181.228.646.414.5085.085.0183.619@5MHz

4 结 论

本文提出了一种采用0.18 μm标准的CMOS工艺的低功耗、高CMRR的伪差分OTA,其采用CMFF技术用于抑制输出节点处的共模信号,以补偿由PD结构引起的CMRR问题.与现有技术的OTA相比,本文所提出的OTA最主要的优点是具有更高的跨导增益,更小的面积成本和更小的附加功耗,该种跨导增益分别是传统FD OTA与PD OTA结构的两倍和四倍.

[1] Rezaei F,Azhari S J.Transconductor linearization based on adaptive biasing of source-degenerative MOS transistors[J].Circuits Systems & Signal Processing,2014,34(4):1-17.

[2] S nchez T,Gal

nchez T,Gal n J,Mu

n J,Mu oz F,et al.A low-power baseband filter based on a 1.2-V 65-nm CMOS bulk-driven linear tunable transconductor[J].Journal of Low Power Electronics,2016,12(3):234-241.

oz F,et al.A low-power baseband filter based on a 1.2-V 65-nm CMOS bulk-driven linear tunable transconductor[J].Journal of Low Power Electronics,2016,12(3):234-241.

[3] Xu C.A novel pseudo differential transconductor for IEEE 802.11 WLANs[J].Analog Integrated Circuits & Signal Processing,2014,81(2):385-391.

[4] Zhang J,Zhang H,Sun Q,et al.A low-noise,low-power amplifier with current-reused OTA for ECG recordings[J].IEEE Transactions on Biomedical Circuits & Systems,2018,12(3):700-709.

[5] Veldandi H,Shaik R A.A 0.3-V pseudo-differential bulk-input OTA for low-frequency applications[J].Circuits Systems & Signal Processing,2018,5:1-23.

[6] Elamien M B,Mahmoud S A.On the design of highly linear CMOS digitally programmable operational transconductance amplifiers for low and high-frequency applications[J].Analog Integrated Circuits & Signal Processing,2018,4:1-17.

[7] Akbari M,Biabanifard S,Asadi S,et al.Design and analysis of DC gain and transconductance boosted recy-cling folded cascode OTA[J].AEUE-International Journal of Electronics and Communications,2014,68(11):1047-1052.

[8] 薛超耀,韩志超,欧健,等.一种恒跨导轨对轨CMOS运算放大器的设计[J].电子科技,2013,26(9):121-123.

(XUE Chao-yao,HAN Zhi-chao,OU Jian,et al.Design of a CMOS operational amplifier with constant-span rail-to-rail[J].Electronic Science and Technology,2013,26(9):121-123.)

[9] 殷万君,白天蕊.改进型折叠式共源共栅运算放大器电路的设计[J].现代电子技术,2012,35(20):167-168.

(YIN Wan-jun,BAI Tian-rui.Design of an improved folded cascode operational amplifier circuit[J].Modern Electronic Technology,2012,35(20):167-168.)

[10] 肖莹慧.全差分结构低功耗CMOS运算放大器设计[J].沈阳工业大学学报,2017,39(6):670-674.

(XIAO Ying-hui.Design of fully differential low power CMOS operational amplifier[J].Journal of Shenyang University of Technology,2017,39(6):670-674.)

[11] 陈炜,景新幸,祁琳娜,等.用于Sigma-Delta调制器的低电压跨导运算放大器[J].电子设计工程,2010,18(5):114-116.

(CHEN Wei,JING Xin-xing,QI Lin-na,et al.Low voltage transconductance operational amplifier for Sigma-Delta modulator[J].Electronic Design Engineering,2010,18(5):114-116.)